Tunnel Field-Effect Transistors (TFETs) are a type of transistor that leverages the quantum mechanical phenomenon of tunneling to switch the current flow on and off. Unlike traditional Field-Effect Transistors (FETs), which rely on thermal injection of carriers over a barrier, TFETs use tunneling through a barrier, enabling them to operate at much lower voltages and power levels.

Working Principle of Tunnel Field-Effect Transistors (TFETs)

The fundamental working principle of TFETs involves quantum tunneling. In a TFET, the source and the channel are separated by a thin barrier. When a voltage is applied to the gate, it modulates the energy bands of the source and the channel. If the gate voltage is high enough, it aligns the energy bands in such a way that electrons can tunnel through the barrier from the source to the channel, thereby turning the transistor on. When the gate voltage is reduced, the energy bands are misaligned, preventing tunneling and turning the transistor off.

Structure of TFETs

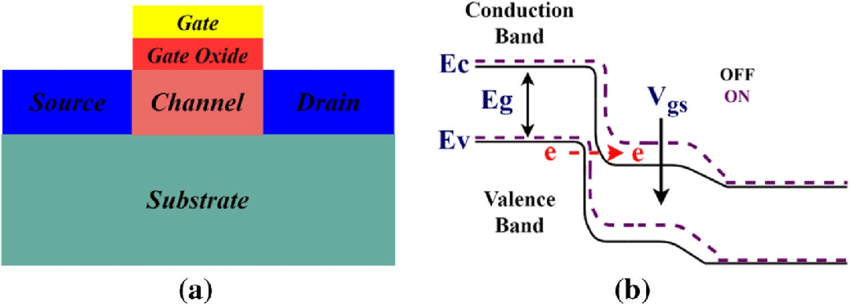

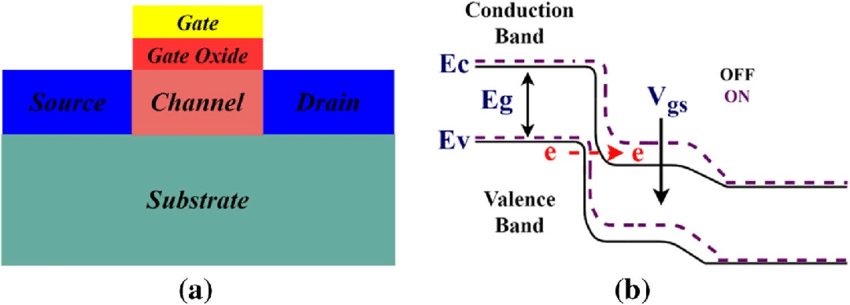

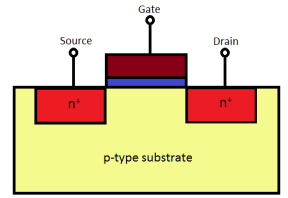

The basic structure of a TFET is similar to that of a conventional Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) but with key differences. A TFET consists of:

Here is a drawing of the structure of a Tunnel Field-Effect Transistor (TFET):

- Source (p-type): This region is heavily doped to create a steep energy gradient necessary for tunneling.

- Drain (n-type): This region is also heavily doped but with an opposite type to the source.

- Channel: The region between the source and drain where the tunneling occurs.

- Gate: Controls the tunneling barrier height and thickness.

Working Principle of Tunnel Field-Effect Transistors (TFETs)

The working principle of Tunnel Field-Effect Transistors (TFETs) is fundamentally different from that of conventional Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). TFETs exploit the quantum mechanical phenomenon of band-to-band tunneling to control the flow of current, enabling them to operate efficiently at lower voltages.

When a voltage is applied to the gate, it modulates the energy bands in the source and the channel. If the gate voltage is high enough, it aligns the energy bands of the source and channel such that the conduction band of the source overlaps with the valence band of the channel. This alignment creates a narrow barrier through which electrons can tunnel. Also, Read: Lithography in Semiconductor Manufacturing: Complete Guide

Quantum Tunneling Mechanism

Step-by-Step Operation

- Off State:

- When the gate voltage is low, the energy bands are misaligned.

- The conduction band of the source is separated from the valence band of the channel by a wide energy gap.

- Electrons cannot tunnel through this wide barrier, and no current flows between the source and drain, keeping the TFET in the off state.

- On State:

- When the gate voltage is increased, the energy bands are modulated.

- The conduction band of the source aligns with the valence band of the channel, creating a narrow tunneling barrier.

- Electrons tunnel through this narrow barrier from the source to the channel and then to the drain, resulting in current flow and turning the TFET on.

Advantages of Tunneling Mechanism

- Low Power Consumption: The tunneling mechanism allows TFETs to operate at much lower voltages compared to MOSFETs, significantly reducing power consumption. This makes TFETs ideal for low-power applications such as mobile devices and wearables.

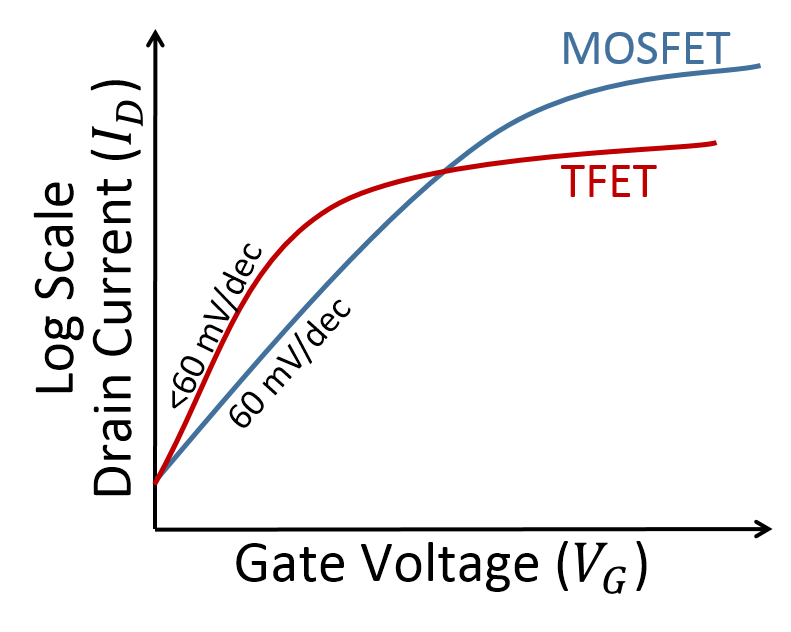

- Sharp Subthreshold Swing: TFETs can achieve a subthreshold swing lower than the 60 mV/decade limit of MOSFETs, allowing for better performance at low voltages. This characteristic enables faster switching and lower leakage currents.

- Scalability: The tunneling mechanism is less affected by short-channel effects, making TFETs more scalable and suitable for future generations of ultra-scaled electronic devices.

Challenges with Tunnel Field-Effect Transistors (TFETs)

Despite the advantages, TFETs face several challenges that need to be addressed:

- Material Selection: The performance of TFETs is highly dependent on the choice of materials. Finding materials with the right bandgap and effective masses for efficient tunneling remains a challenge.

- Fabrication Complexity: The precise control required in the doping process and material deposition makes the fabrication of TFETs more complex than conventional transistors.

- High Current Handling: While TFETs are excellent for low-power applications, their performance at high current levels needs improvement for broader adoption in high-performance computing.

Tunnel Field-Effect Transistors (TFETs) are emerging as a crucial technology in modern electronics due to their unique operational characteristics and significant advantages over conventional transistors. Their importance lies in their potential to address the growing demands for energy efficiency, miniaturization, and performance in various electronic applications.

1. Energy Efficiency

Low Power Consumption: One of the primary benefits of TFETs is their low power consumption. Traditional MOSFETs require relatively high voltages to switch on and off, leading to higher energy usage. In contrast, TFETs operate efficiently at much lower voltages due to their reliance on quantum tunneling. This characteristic makes them ideal for battery-powered devices, reducing the frequency of recharging and extending battery life in smartphones, wearables, and other portable electronics.

Reduction in Heat Generation: Lower power consumption translates directly into less heat generation. Heat management is a significant challenge in modern electronics, particularly in compact devices where effective heat dissipation is difficult. TFETs’ lower energy usage helps mitigate thermal issues, enhancing the reliability and longevity of electronic components.

2. Performance Enhancement

Sharp Subthreshold Swing: TFETs can achieve a subthreshold swing below the 60 mV/decade limit of conventional MOSFETs. This results in faster switching times and improved performance at low operating voltages. Such characteristics are particularly advantageous in high-speed computing applications and for maintaining performance as devices continue to shrink in size.

Scalability: As device dimensions decrease, conventional transistors face challenges such as short-channel effects, which degrade performance. TFETs, however, are less affected by these issues due to their tunneling mechanism. This makes TFETs more scalable, supporting the continued miniaturization of electronic components and adherence to Moore’s Law, which predicts the doubling of transistors on a microchip approximately every two years. Also, Read: What is Edge Computing? Complete Guide

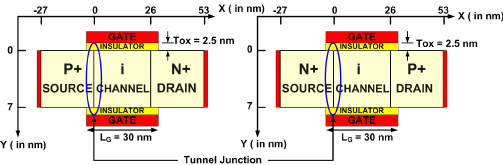

Basic Structure Components of TFETs: Source, Drain, Gate, and Channel

Tunnel Field-Effect Transistors (TFETs) are composed of four fundamental components: the source, drain, gate, and channel. Each of these components plays a crucial role in the operation of the TFET, working together to enable the tunneling mechanism that distinguishes TFETs from traditional transistors like MOSFETs. Here’s a detailed look at each of these components:

1. Source

Definition: The source is one of the two main terminals of the TFET where the charge carriers (electrons or holes) originate.

Doping Characteristics:

- The source is heavily doped with one type of dopant (e.g., p-type for holes or n-type for electrons).

- This heavy doping creates a high concentration of charge carriers, resulting in a steep energy gradient necessary for the tunneling process.

Role in Tunneling:

- In a p-type source TFET, the source has a high concentration of holes.

- When a suitable gate voltage is applied, it aligns the energy bands in such a way that allows electrons from the conduction band of the source to tunnel through the barrier into the channel.

2. Drain

Definition: The drain is the terminal where the charge carriers exit the TFET after traveling through the channel.

Doping Characteristics:

- The drain is also heavily doped, but with the opposite type of dopant compared to the source (e.g., n-type for a p-type source).

- This creates a region with a high concentration of the opposite type of charge carriers.

Role in Tunneling:

- In a p-type source TFET, the drain is n-type, providing a sink for the electrons that have tunneled through the channel.

- The alignment of the energy bands between the source and drain, controlled by the gate voltage, facilitates the flow of carriers from the source to the drain through the channel.

3. Gate

Definition: The gate is a terminal that controls the current flow between the source and drain by modulating the energy bands in the channel region.

Structure and Material:

- The gate is typically made of a conductive material, such as polysilicon or metal, and is separated from the channel by a thin insulating layer (gate oxide).

Role in Tunneling:

- Applying a voltage to the gate modulates the energy bands in the source and channel regions.

- When the gate voltage is high enough, it aligns the energy bands of the source and channel, creating a narrow tunneling barrier.

- This alignment allows charge carriers to tunnel through the barrier from the source to the channel, enabling current flow.

4. Channel

Definition: The channel is the region between the source and drain through which the charge carriers travel after tunneling.

Structure:

- The channel is lightly doped or intrinsic, creating a controlled environment for the tunneling process.

Role in Tunneling:

- The channel plays a crucial role in the tunneling mechanism. When the gate voltage aligns the energy bands, the channel acts as a pathway for the charge carriers to move from the source to the drain.

- The width and properties of the channel determine the efficiency and characteristics of the tunneling process.

Interaction of Components

Tunneling Mechanism:

- The source, with its high concentration of carriers, provides the initial charge carriers.

- The gate voltage modulates the energy bands, aligning the source and channel bands to create a tunneling barrier.

- The channel serves as the medium through which carriers tunnel, controlled by the gate’s influence.

- The drain collects the tunneled carriers, completing the circuit and allowing current to flow.

Energy Band Diagram:

- At low gate voltage, the energy bands of the source and channel are misaligned, preventing tunneling and thus current flow.

- As the gate voltage increases, it lowers the energy barrier in the channel, aligning the conduction band of the source with the valence band of the channel.

- This alignment facilitates tunneling, allowing carriers to move from the source through the channel to the drain, thus turning the TFET on. Also, Read: What is Wireless Power Transfer (WPT) Technology?

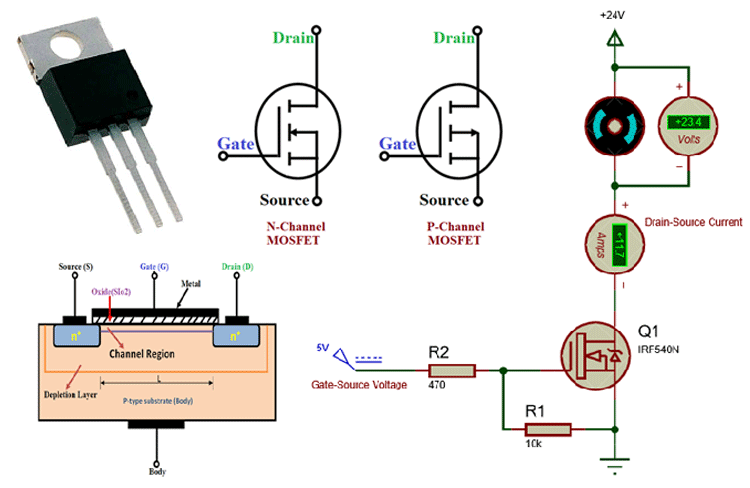

Comparison of TFETs with Conventional Transistors

Tunnel Field-Effect Transistors (TFETs) and conventional transistors, such as Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), are key components in modern electronics. However, they operate based on different principles and exhibit distinct characteristics. Below, we compare TFETs with conventional transistors in terms of their working principles, structure, performance, power consumption, scalability, and applications.

1. Working Principles

Conventional Transistors (MOSFETs):

- Operation: MOSFETs operate by controlling the flow of carriers (electrons or holes) through a channel between the source and drain terminals using an electric field applied via the gate.

- Mechanism: Current flow in MOSFETs is controlled by the thermionic emission of carriers over a potential barrier. When a sufficient gate voltage is applied, it inverts the type of semiconductor under the gate (forming a conductive channel).

TFETs:

- Operation: TFETs operate by leveraging the quantum mechanical phenomenon of tunneling. The gate voltage modulates the energy bands to create a tunneling barrier through which carriers can pass.

- Mechanism: When the gate voltage aligns the conduction band of the source with the valence band of the channel, carriers tunnel through the barrier, enabling current flow.

2. Structure

Conventional Transistors (MOSFETs):

- Components: Source, drain, gate, and channel, all typically made of the same semiconductor material.

- Channel Formation: The channel is formed by inverting the semiconductor type under the gate through electrostatic control.

TFETs:

- Components: Source, drain, gate, and channel, but the source and drain can be made of different semiconductor materials in heterojunction TFETs.

- Tunneling Junction: The source and channel are designed to create a tunneling junction that allows for efficient quantum tunneling.

3. Performance Characteristics

Conventional Transistors (MOSFETs):

- Subthreshold Swing: Limited by the thermal voltage, typically around 60 mV/decade at room temperature.

- On-State Current (I<sub>ON</sub>): Generally higher due to the efficient carrier injection.

- Switching Speed: Faster switching times but higher power consumption at low voltages.

TFETs:

- Subthreshold Swing: Can achieve values lower than 60 mV/decade due to the tunneling mechanism, leading to more efficient switching at low voltages.

- On-State Current (I<sub>ON</sub>): Generally lower than MOSFETs due to the limitations in tunneling efficiency.

- Switching Speed: Potentially slower switching due to the reliance on quantum tunneling but improved energy efficiency.

4. Power Consumption

Conventional Transistors (MOSFETs):

- Power Efficiency: Higher power consumption due to the need for higher gate voltages to achieve significant current flow.

- Leakage Current: Higher off-state leakage current, leading to increased standby power consumption.

TFETs:

- Power Efficiency: Significantly lower power consumption due to efficient operation at lower voltages.

- Leakage Current: Lower off-state leakage current, reducing standby power consumption and enhancing energy efficiency.

5. Scalability

Conventional Transistors (MOSFETs):

- Short-Channel Effects: More susceptible to short-channel effects as device dimensions shrink, leading to performance degradation.

- Scaling Limits: Faces physical and material limitations in further scaling down.

TFETs:

- Short-Channel Effects: Less affected by short-channel effects due to the tunneling mechanism, allowing for better scalability.

- Future Potential: Better suited for ultra-scaled devices and advanced technological nodes.

6. Applications

Conventional Transistors (MOSFETs):

- General Use: Widely used in a broad range of applications including digital logic circuits, analog devices, and power electronics.

- Performance-Critical: Preferred in high-performance computing where speed is critical despite higher power consumption.

TFETs:

- Low-Power Applications: Ideal for applications requiring high energy efficiency, such as portable electronics, IoT devices, and medical implants.

- Emerging Technologies: Suitable for advanced applications where low power and scalability are critical, such as ultra-low-power sensors and future computing paradigms. Also, Read: What is Digital Twin Technology? Complete Guide

Summary of Differences (Conventional Transistors (MOSFETs) vs TFETs)

| Feature | Conventional Transistors (MOSFETs) | TFETs |

| Working Principle | Thermionic emission over a barrier | Quantum tunneling through a barrier |

| Structure | Single semiconductor material | Potentially different materials (heterojunction) |

| Subthreshold Swing | ≥ 60 mV/decade | < 60 mV/decade |

| On-State Current (I<sub>ON</sub>) | Higher | Lower |

| Power Consumption | Higher | Lower |

| Leakage Current | Higher | Lower |

| Short-Channel Effects | More susceptible | Less susceptible |

| Switching Speed | Faster | Potentially slower |

| Scalability | Limited | Better suited for scaling |

| Applications | Broad range, high-performance | Low-power, emerging technologies |

Versatility in Applications

Internet of Things (IoT): The IoT ecosystem relies on numerous interconnected devices, many of which are battery-operated and require energy-efficient components. TFETs’ low power operation makes them well-suited for IoT applications, enabling longer device lifespans and reducing the need for frequent maintenance or battery replacements.

Wearable Technology: Wearable devices, such as fitness trackers, smartwatches, and medical monitors, benefit significantly from the low power consumption and compact size of TFETs. These transistors support the development of lightweight, efficient, and long-lasting wearable electronics that can operate for extended periods on a single charge.

Mobile Devices: Smartphones and tablets are continually evolving to include more features while maintaining or improving battery life. TFETs can play a critical role in achieving this balance by providing efficient power management and performance improvements, enabling the integration of more advanced functionalities without compromising battery life.

High-Performance Computing: Although still under research, TFETs hold promise for use in processors and other high-performance computing components. Their potential for high-speed operation at low voltages could lead to more energy-efficient data centers and computing infrastructures, addressing the ever-increasing demand for computational power and data processing capabilities.

Environmental Impact

Sustainability: With the growing emphasis on sustainability and reducing carbon footprints, the adoption of energy-efficient technologies like TFETs is crucial. By lowering the power requirements of electronic devices, TFETs contribute to reducing overall energy consumption, which in turn decreases greenhouse gas emissions associated with electricity production.

Extended Device Lifespan: Lower power consumption and reduced heat generation can lead to longer-lasting electronic devices. This reduces electronic waste and the environmental impact associated with the frequent replacement and disposal of electronic products.

Examples of Modern Equipment Using TFETs

While TFETs are still primarily in the research and development phase, there are several emerging applications and prototype devices that highlight their potential use in modern equipment. Below are some examples where TFETs could significantly impact or are being explored for integration:

1. Low-Power Mobile Devices

Smartphones and Tablets: TFETs are being investigated for use in processors and power management circuits within smartphones and tablets. Their low power consumption can extend battery life, making these devices more energy-efficient and capable of supporting advanced features without rapid battery drain.

2. Wearable Technology

Smartwatches and Fitness Trackers: Wearables benefit greatly from the energy efficiency of TFETs. By integrating TFETs, these devices can operate longer on a single charge, enhancing user convenience and reducing the need for frequent recharging.

Medical Monitors: Continuous health monitoring devices, such as heart rate monitors and glucose sensors, require low-power operation to ensure long-term usage without frequent battery replacement. TFETs’ low power characteristics are ideal for these applications, making medical monitoring more reliable and user-friendly.

3. Internet of Things (IoT) Devices

Smart Home Devices: TFETs can be used in various smart home devices, such as sensors, smart thermostats, and security cameras. These devices often rely on battery power or energy harvesting methods, making the low power consumption of TFETs highly advantageous.

Environmental Sensors: IoT sensors deployed for environmental monitoring (e.g., air quality sensors, weather stations) need to operate for extended periods in remote locations. TFETs can help achieve longer operational lifespans, reducing maintenance and battery replacement frequency.

4. Energy-Efficient Computing

Data Centers: TFETs are being explored for use in server processors and memory components within data centers. Their potential to operate at lower voltages can lead to significant energy savings, reducing operational costs and environmental impact.

High-Performance Computing (HPC): Supercomputers and HPC systems could benefit from the integration of TFETs to achieve higher computational efficiency with lower power requirements, enabling more powerful and energy-efficient computing solutions.

5. Portable Electronics

Laptops and Ultrabooks: TFETs can enhance battery life and reduce heat generation in portable computers, making them more efficient and comfortable to use. This is particularly important for ultrabooks and other compact devices where battery space and thermal management are critical concerns.

E-Readers and Portable Media Players: Devices designed for prolonged use, such as e-readers and media players, can achieve longer battery life and better performance with TFETs, providing a more enjoyable user experience.

6. Medical Implants

Implantable Medical Devices: TFETs are being studied for use in medical implants, such as pacemakers and neural stimulators. The low-power operation of TFETs is crucial for these applications, where battery longevity and reliable performance are paramount.

7. Automotive Electronics

Advanced Driver-Assistance Systems (ADAS): In the automotive industry, TFETs can be used in various electronic control units (ECUs) and sensors that support ADAS features, enhancing vehicle safety and efficiency.

Electric Vehicle (EV) Power Management: TFETs can improve the efficiency of power management systems in electric vehicles, extending driving range and reducing energy consumption.

Differences in Structure Compared to Conventional FETs

Tunnel Field-Effect Transistors (TFETs) and conventional Field-Effect Transistors (FETs), such as Metal-Oxide-Semiconductor FETs (MOSFETs), share some structural similarities but also exhibit critical differences that enable their unique operational characteristics. Understanding these differences is essential to appreciate the advantages and challenges associated with TFETs. Here are the key structural differences between TFETs and conventional FETs:

1. Source and Drain Doping

Conventional FETs (MOSFETs):

- In a MOSFET, both the source and drain are typically doped with the same type of carrier (either n-type for NMOS or p-type for PMOS).

- The source and drain regions are moderately doped to create a well-defined channel when the gate voltage is applied.

TFETs:

- In TFETs, the source and drain regions are heavily doped with opposite types of dopants (e.g., the source is p-type and the drain is n-type for a p-type source TFET).

- This heavy and opposite doping creates a steep energy gradient necessary for the tunneling mechanism.

2. Channel Region

Conventional FETs (MOSFETs):

- The channel in a MOSFET is formed between the source and drain when a voltage is applied to the gate, creating an electric field that inverts the semiconductor type under the gate (e.g., in an NMOS, a positive gate voltage attracts electrons to form an n-type channel in a p-type substrate).

- The channel length and doping are optimized to balance performance and scalability.

TFETs:

- The channel in a TFET is lightly doped or intrinsic, allowing the tunneling mechanism to dominate the current transport.

- The channel region in TFETs is designed to facilitate the alignment of energy bands for tunneling, rather than the formation of a conductive channel through inversion.

3. Gate Structure and Function

Conventional FETs (MOSFETs):

- The gate in a MOSFET is typically a metal or polysilicon layer insulated from the channel by a thin layer of gate oxide (silicon dioxide).

- Applying a voltage to the gate controls the formation of the conductive channel by creating an electric field that attracts carriers to the semiconductor-oxide interface.

TFETs:

- The gate in a TFET also controls the channel but operates differently. The gate voltage modulates the energy bands in the source and channel regions to facilitate tunneling.

- The gate in a TFET has a similar physical structure (conductive material insulated from the channel) but its role is to align the energy bands for tunneling rather than creating a conductive inversion layer.

4. Energy Band Alignment and Operation

Conventional FETs (MOSFETs):

- In MOSFETs, current flows through the channel when an appropriate gate voltage creates a conductive path by inverting the type of semiconductor in the channel region.

- The operation relies on the thermionic emission of carriers over a potential barrier.

TFETs:

- In TFETs, current flows when the gate voltage aligns the conduction band of the source with the valence band of the channel, creating a narrow tunneling barrier.

- The operation relies on quantum mechanical tunneling of carriers through the energy barrier rather than over it.

5. Subthreshold Swing and Switching Behavior

Conventional FETs (MOSFETs):

- MOSFETs have a subthreshold swing limit of 60 mV/decade at room temperature, which determines how sharply the transistor can switch from off to on.

- The switching behavior is governed by thermionic emission and is less efficient at lower voltages.

TFETs:

- TFETs can achieve a subthreshold swing below 60 mV/decade, allowing for more efficient switching at lower voltages.

- The sharp switching behavior in TFETs is due to the tunneling mechanism, which is less affected by thermal limitations.

Also, Read: Trends in Welding Technology

Summary of Structural Differences Conventional FETs (MOSFETs) Vs Tunnel Field-Effect Transistors (TFETs)

| Component | Conventional FETs (MOSFETs) | TFETs |

| Source/Drain Doping | Same type (e.g., both n-type for NMOS) | Opposite types (e.g., p-type source, n-type drain) |

| Channel Region | Formed by gate-induced inversion | Lightly doped/intrinsic, facilitates tunneling |

| Gate Structure | Metal/poly gate insulated by gate oxide | Similar structure, but controls energy band alignment for tunneling |

| Energy Band Alignment | Controlled by gate to form conductive channel | Controlled by gate to align bands for tunneling |

| Subthreshold Swing | Limited to 60 mV/decade | Can be less than 60 mV/decade due to tunneling |

| Operation Mechanism | Thermionic emission over barrier | Quantum tunneling through barrier |

Differences Between n-Type and p-Type TFETs

Tunnel Field-Effect Transistors (TFETs) come in two main types: n-Type and p-Type. The primary distinction between these two types lies in the doping of their source and drain regions, which determines the type of charge carriers (electrons or holes) involved in the tunneling process.

Below are the key differences between n-Type and p-Type TFETs:

1. Doping Configuration

n-Type TFETs:

- Source: Heavily p-type doped, providing a high concentration of holes.

- Drain: Heavily n-type doped, providing a high concentration of electrons.

- Charge Carriers: Electrons are the majority carriers that tunnel from the valence band of the p-type source to the conduction band of the n-type channel and drain.

p-Type TFETs:

- Source: Heavily n-type doped, providing a high concentration of electrons.

- Drain: Heavily p-type doped, providing a high concentration of holes.

- Charge Carriers: Holes are the majority carriers that tunnel from the conduction band of the n-type source to the valence band of the p-type channel and drain.

Also, Read: Trends in Electrical Cables

2. Tunneling Mechanism

n-Type TFETs:

- Tunneling Process: When a positive gate voltage is applied, it lowers the conduction band edge of the channel to align with the valence band edge of the source. This alignment creates a narrow barrier through which electrons can tunnel.

- Direction of Tunneling: Electrons tunnel from the source to the channel and then to the drain.

p-Type TFETs:

- Tunneling Process: When a negative gate voltage is applied, it raises the valence band edge of the channel to align with the conduction band edge of the source. This alignment creates a narrow barrier through which holes can tunnel.

- Direction of Tunneling: Holes tunnel from the source to the channel and then to the drain.

3. Voltage Polarity for Operation

n-Type TFETs:

- Gate Voltage: Requires a positive gate voltage to facilitate tunneling of electrons.

- Source-Drain Voltage: Typically, a positive source-drain voltage is applied for electron flow from the source to the drain.

p-Type TFETs:

- Gate Voltage: Requires a negative gate voltage to facilitate tunneling of holes.

- Source-Drain Voltage: Typically, a negative source-drain voltage is applied for hole flow from the source to the drain.

4. Typical Applications

n-Type TFETs:

- Low-Power Electronics: Suitable for applications where energy efficiency is critical, such as mobile devices, wearables, and IoT sensors.

- High-Performance Computing: Potential use in data centers and supercomputers for energy-efficient processing.

- Automotive Electronics: Used in advanced driver-assistance systems (ADAS) and electric vehicle (EV) power management.

p-Type TFETs:

- Low-Power Electronics: Ideal for similar applications as n-Type TFETs, including mobile devices, wearables, and IoT sensors.

- Medical Devices: Useful in implantable electronics and wearable health monitors due to their low power consumption.

- Automotive Electronics: Can be applied in ADAS and EV power management, similar to n-Type TFETs, but with different circuit design considerations.

Summary of Differences (n-Type TFETs vs p-Type TFETs)

| Feature | n-Type TFETs | p-Type TFETs |

| Source Doping | Heavily p-type (holes) | Heavily n-type (electrons) |

| Drain Doping | Heavily n-type (electrons) | Heavily p-type (holes) |

| Majority Carriers | Electrons | Holes |

| Gate Voltage Polarity | Positive | Negative |

| Tunneling Mechanism | Electrons tunnel from source to drain | Holes tunnel from source to drain |

| Typical Applications | Mobile devices, IoT sensors, data centers | Mobile devices, medical implants, ADAS |

Heterojunction TFETs: Definition and Benefits

Definition

Heterojunction TFETs are a type of Tunnel Field-Effect Transistor (TFET) that utilize different semiconductor materials for the source and channel regions. This contrasts with homojunction TFETs, where the same semiconductor material is used throughout the device. The heterojunction approach exploits the unique properties of different materials to optimize the tunneling process, enhancing the overall performance of the TFET.

Benefits of Heterojunction TFETs

1. Enhanced Tunneling Efficiency:

- The use of different materials allows for better alignment of energy bands between the source and channel, facilitating more efficient tunneling of charge carriers (electrons or holes).

- By selecting materials with appropriate bandgap energies, heterojunction TFETs can achieve lower tunneling barriers, which reduces the voltage required to initiate tunneling and improves the subthreshold swing.

2. Improved On-State Current:

- Heterojunction TFETs typically exhibit higher on-state current (I<sub>ON</sub>) compared to homojunction TFETs. This is due to the optimized band alignment that enhances carrier injection from the source to the channel.

- The higher on-state current translates to better performance in terms of speed and responsiveness, making heterojunction TFETs suitable for high-performance applications.

3. Lower Off-State Leakage:

- The use of materials with appropriate bandgap differences can help in achieving lower off-state leakage currents. This is particularly important for low-power applications where minimizing power consumption during the off state is crucial.

- Reduced leakage currents contribute to the overall energy efficiency of the device, extending battery life in portable electronics and improving the reliability of low-power systems.

4. Greater Design Flexibility:

- Heterojunction TFETs offer more flexibility in material selection, allowing for the optimization of device characteristics based on specific application requirements.

- This flexibility can be leveraged to tailor the electrical properties of the TFET, such as threshold voltage, drive current, and switching speed, to meet the demands of different electronic systems.

Comparison with Homojunction TFETs

1. Material Composition:

Homojunction TFETs:

- Utilize the same semiconductor material for both the source and channel regions.

- Common materials include silicon (Si) or germanium (Ge), which simplify the fabrication process but may limit the optimization of tunneling properties.

Heterojunction TFETs:

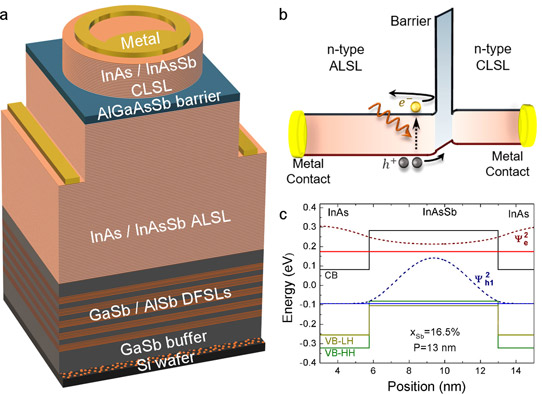

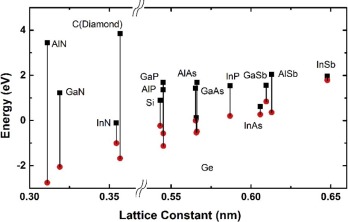

- Employ different semiconductor materials for the source and channel regions, such as combinations of III-V compounds (e.g., InAs/GaAs or GaSb/InAs).

- This material diversity allows for better band alignment and more efficient tunneling characteristics.

2. Band Alignment:

Homojunction TFETs:

- The band alignment is determined by the intrinsic properties of a single material, which may not be optimal for tunneling efficiency.

- Tunneling efficiency is often limited by the need to balance the material’s bandgap and effective mass.

Heterojunction TFETs:

- By choosing materials with complementary band structures, heterojunction TFETs can achieve superior band alignment, reducing the tunneling barrier and improving carrier injection.

- This optimized band alignment enhances both the on-state current and subthreshold swing, leading to better overall device performance.

3. Performance Characteristics:

Homojunction TFETs:

- Typically exhibit lower on-state current (I<sub>ON</sub>) and higher off-state leakage compared to heterojunction TFETs.

- The performance is constrained by the material’s inherent properties, which may not be ideal for all applications.

Heterojunction TFETs:

- Offer higher on-state current (I<sub>ON</sub>) and lower off-state leakage, making them more suitable for high-performance and low-power applications.

- The ability to tailor material properties leads to improved device performance, particularly in terms of energy efficiency and switching speed.

4. Fabrication Complexity:

Homojunction TFETs:

- Generally simpler to fabricate due to the use of a single semiconductor material, which can streamline the manufacturing process.

- This simplicity can result in lower production costs and easier integration with existing semiconductor fabrication technologies.

Heterojunction TFETs:

- More complex to fabricate because they require the integration of different semiconductor materials, which can involve advanced epitaxial growth techniques and precise material interfaces.

- The increased fabrication complexity can lead to higher production costs and challenges in ensuring material compatibility and interface quality.

Also, Read: Plastic Trends in USA (Specific Use in Automotive Sector)

Summary of Differences (Homojunction TFETs vs Heterojunction TFETs)

| Feature | Homojunction TFETs | Heterojunction TFETs |

| Material Composition | Single semiconductor material | Different semiconductor materials |

| Band Alignment | Limited by single material properties | Optimized by selecting complementary materials |

| On-State Current (I<sub>ON</sub>) | Lower | Higher |

| Off-State Leakage | Higher | Lower |

| Performance Characteristics | Limited by single material’s properties | Enhanced by optimized band alignment |

| Fabrication Complexity | Simpler, lower cost | More complex, higher cost |

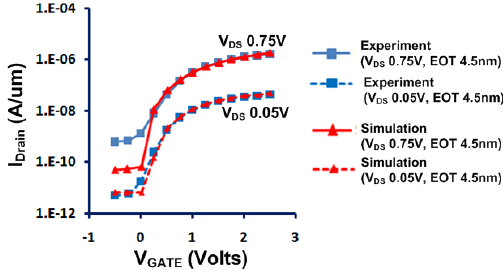

Subthreshold Swing in TFETs and Conventional Transistors

Definition of Subthreshold Swing

Subthreshold Swing (SS) is a key parameter in transistors that measures the efficiency with which the device can switch from the off state to the on state. It is defined as the amount of gate voltage required to increase the drain current by one order of magnitude (typically measured in millivolts per decade, mV/decade). Mathematically, it can be expressed as:

𝑆𝑆=𝑑𝑉𝐺(log𝐼𝐷)SS=d(logID)dVG

where 𝑉𝐺VG is the gate voltage and 𝐼𝐷ID is the drain current.

Subthreshold Swing in Conventional Transistors (MOSFETs)

MOSFETs:

- Thermionic Emission: In MOSFETs, the subthreshold swing is fundamentally limited by the thermionic emission of carriers over a potential barrier. The minimum achievable subthreshold swing at room temperature is approximately 60 mV/decade, due to thermal effects.

- Limitations: This 60 mV/decade limit is known as the “Boltzmann limit” and is a consequence of the thermally activated nature of carrier transport in MOSFETs.

- Equation: For MOSFETs, the subthreshold swing is given by:

𝑆𝑆=𝑘𝑇𝑞ln(10)(1+𝐶𝑑𝐶𝑜𝑥)SS=qkTln(10)(1+CoxCd)

where 𝑘k is Boltzmann’s constant, 𝑇T is the absolute temperature, 𝑞q is the charge of an electron, 𝐶𝑑Cd is the depletion capacitance, and 𝐶𝑜𝑥Cox is the gate oxide capacitance.

Subthreshold Swing in TFETs

TFETs:

- Quantum Tunneling: In TFETs, the subthreshold swing is determined by the quantum tunneling mechanism rather than thermionic emission. This allows TFETs to achieve a subthreshold swing lower than the 60 mV/decade limit.

- Lower SS: TFETs can potentially reach subthreshold swings much lower than the theoretical limit for MOSFETs, often approaching 30 mV/decade or even lower at room temperature. This is because the current in TFETs depends on the alignment of energy bands and the tunneling probability, which can be modulated more efficiently by the gate voltage.

- Advantages: A lower subthreshold swing means that TFETs can turn on more abruptly, enabling better performance at lower operating voltages and reducing leakage current in the off state.

Importance of Subthreshold Swing

1. Power Efficiency:

- Lower Operating Voltage: Devices with a lower subthreshold swing can operate at lower gate voltages, reducing overall power consumption. This is critical for battery-operated devices, such as mobile phones and IoT sensors, where energy efficiency is paramount.

- Reduced Leakage Current: A sharp subthreshold swing also means lower leakage current when the device is off, contributing to reduced standby power consumption and enhancing energy efficiency.

2. Performance:

- Fast Switching: A lower subthreshold swing allows transistors to switch between on and off states more quickly. This can improve the speed and performance of digital circuits, making TFETs suitable for high-speed applications.

- Scalability: As device dimensions shrink, maintaining a low subthreshold swing becomes increasingly important to ensure that transistors can operate effectively at smaller scales and lower voltages.

Comparison of Subthreshold Swing in MOSFETs and TFETs

| Feature | MOSFETs | TFETs |

| Subthreshold Swing | Limited to around 60 mV/decade | Can be lower than 60 mV/decade |

| Mechanism | Thermionic emission over a barrier | Quantum tunneling through a barrier |

| Temperature Dependence | Strongly temperature-dependent | Less dependent on temperature |

| Power Efficiency | Higher operating voltages, more power consumption | Lower operating voltages, more energy-efficient |

| Switching Speed | Slower switching due to higher SS | Faster switching due to lower SS |

| Leakage Current | Higher leakage current in off state | Lower leakage current in off state |

Challenges and Considerations

Fabrication Complexity:

- Achieving and maintaining a low subthreshold swing in TFETs requires precise control over material properties and device fabrication processes. The interface quality, doping concentrations, and material selection all play critical roles in determining the subthreshold swing.

Material Selection:

- The choice of materials for the source, channel, and drain regions is crucial in optimizing the subthreshold swing in TFETs. Heterojunction TFETs, which use different materials for these regions, can achieve better performance but also introduce fabrication complexities.

Temperature Sensitivity:

- While TFETs are less sensitive to temperature variations compared to MOSFETs, the performance of TFETs can still be affected by changes in temperature, particularly in terms of band alignment and tunneling efficiency.

Performance Benefits in Low-Voltage Operation

Tunnel Field-Effect Transistors (TFETs) offer significant performance benefits in low-voltage operation compared to conventional transistors such as MOSFETs. These benefits stem from the unique mechanism of quantum tunneling employed by TFETs, which allows them to achieve efficient switching and high performance at lower supply voltages.

Here are the key performance benefits of TFETs in low-voltage operation:

1. Lower Power Consumption

Reduced Voltage Requirements:

- TFETs can operate effectively at much lower gate voltages compared to MOSFETs. This is because the tunneling process requires less energy to initiate current flow.

- Lower operating voltages translate directly to reduced power consumption, which is crucial for battery-powered devices such as smartphones, wearables, and IoT sensors.

Energy Efficiency:

- The ability to switch on and off at lower voltages minimizes the energy used per operation. This enhances the overall energy efficiency of electronic circuits, extending battery life and reducing energy costs in larger systems.

2. Improved Subthreshold Swing

Sharp Switching Characteristics:

- TFETs exhibit a subthreshold swing lower than the 60 mV/decade limit of MOSFETs. This allows TFETs to switch more abruptly from off to on states.

- A steeper subthreshold swing ensures that the device can operate efficiently even at low voltages, maintaining high performance without the need for higher power levels.

Reduced Leakage Current:

- The lower subthreshold swing also means that TFETs have significantly reduced leakage currents when in the off state. This is particularly beneficial for low-power and standby operations, where minimizing power loss is critical.

3. Enhanced Scalability

Minimized Short-Channel Effects:

- As transistor dimensions continue to shrink, short-channel effects become a significant challenge for conventional MOSFETs, leading to performance degradation and increased power consumption.

- TFETs are less susceptible to short-channel effects due to their reliance on quantum tunneling rather than thermionic emission. This makes TFETs more scalable for future generations of ultra-miniaturized electronic devices.

Potential for Continued Moore’s Law Scaling:

- The improved scalability of TFETs supports the continuation of Moore’s Law, allowing for the integration of more transistors on a chip without compromising performance or increasing power consumption excessively.

4. Better Performance at Low Voltage

High On-State Current (I<sub>ON</sub>):

- Although TFETs typically have a lower on-state current compared to MOSFETs, advances in heterojunction and material engineering are closing this gap. Optimized TFET designs can achieve competitive or even superior on-state currents at low voltages.

- This ensures that TFETs can deliver the necessary drive currents for high-speed and high-performance applications while operating at lower power levels.

Enhanced Signal Integrity:

- The sharp switching characteristics of TFETs at low voltages contribute to better signal integrity in digital circuits. This reduces the likelihood of errors and improves the reliability of electronic systems, particularly in low-voltage and low-power environments.

Also, Read: Wastewater Coagulation: Is an efficient water treatment method?

5. Applications in Low-Power Electronics

Mobile and Portable Devices:

- TFETs are ideal for mobile and portable electronics that require extended battery life and efficient power usage. Their low-voltage operation helps maximize battery efficiency, supporting longer device usage between charges.

IoT and Sensor Networks:

- The low power consumption and efficient low-voltage operation of TFETs make them well-suited for Internet of Things (IoT) devices and sensor networks. These applications often rely on energy harvesting or limited power sources, making the energy efficiency of TFETs a critical advantage.

Wearable Technology:

- Wearables, such as fitness trackers and smartwatches, benefit from the reduced power consumption and enhanced performance of TFETs at low voltages. This enables smaller, lighter, and more efficient designs, improving user experience and device functionality.

Scaling Potential of TFETs

As the demand for smaller, more powerful, and energy-efficient electronic devices continues to grow, the scaling potential of transistors becomes increasingly critical. Tunnel Field-Effect Transistors (TFETs) offer significant advantages in terms of scaling potential, addressing many of the challenges faced by conventional transistors like MOSFETs. Here, we explore the scaling potential of TFETs, the factors contributing to their scalability, and the implications for future technology.

1. Reduced Short-Channel Effects

Short-Channel Effects (SCEs):

- SCEs occur when the channel length of a transistor is comparable to the depletion regions of the source and drain, leading to undesirable effects such as threshold voltage roll-off, drain-induced barrier lowering (DIBL), and increased leakage currents.

- In conventional MOSFETs, SCEs become more pronounced as device dimensions shrink, limiting further scaling and degrading performance.

TFETs and SCEs:

- TFETs are less susceptible to SCEs due to their unique operating mechanism based on quantum tunneling rather than thermionic emission.

- The tunneling process in TFETs is less dependent on the physical dimensions of the channel, allowing for better control over SCEs even at very small scales.

- This intrinsic advantage makes TFETs more suitable for continued scaling down to nanometer dimensions.

2. Improved Subthreshold Swing

Subthreshold Swing in MOSFETs:

- The subthreshold swing (SS) in MOSFETs is limited by the thermal voltage, typically around 60 mV/decade at room temperature.

- This limitation hinders the ability to achieve low-voltage operation and efficient switching as device dimensions decrease.

Subthreshold Swing in TFETs:

- TFETs can achieve subthreshold swings significantly lower than the 60 mV/decade limit, thanks to the tunneling mechanism.

- A lower SS allows for sharper switching transitions, which is crucial for maintaining performance and reducing power consumption in scaled-down devices.

- Enhanced subthreshold swing also enables TFETs to operate effectively at lower supply voltages, which is essential for scaling.

3. Material and Structural Flexibility

Heterojunction Design:

- TFETs can utilize different semiconductor materials for the source and channel regions, known as heterojunction TFETs. This flexibility allows for better band alignment and more efficient tunneling.

- The ability to select materials with complementary properties enhances the performance and scalability of TFETs.

Advanced Materials:

- Incorporating advanced materials such as III-V compounds, germanium, and two-dimensional materials (e.g., graphene, transition metal dichalcogenides) can further improve the tunneling efficiency and scaling potential of TFETs.

- These materials offer superior electronic properties, such as high mobility and optimal bandgap energies, which are advantageous for scaling.

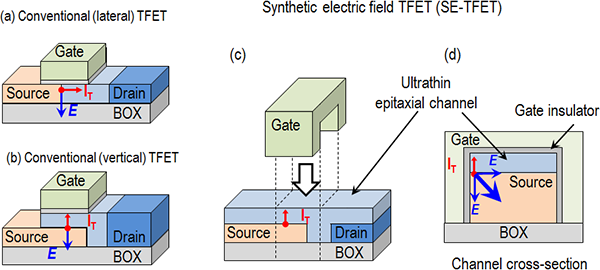

Innovative Structures:

- Novel TFET structures, such as vertical TFETs, gate-all-around (GAA) TFETs, and nanowire TFETs, provide additional avenues for scaling.

- These structures can effectively manage electrostatic control and reduce leakage currents, making them suitable for ultra-scaled device architectures.

4. Lower Power Consumption

Power Efficiency:

- TFETs inherently operate at lower voltages than MOSFETs, reducing overall power consumption.

- Lower power consumption is critical for scaling, as it mitigates issues related to heat dissipation and energy efficiency in densely packed integrated circuits.

Reduced Leakage:

- TFETs exhibit lower off-state leakage currents due to their sharp subthreshold swing and efficient tunneling mechanism.

- Reduced leakage is essential for maintaining energy efficiency and reliability in scaled-down devices, particularly in standby and low-power modes.

5. Compatibility with Emerging Technologies

Integration with CMOS Technology:

- TFETs can be integrated with existing CMOS fabrication processes, facilitating the transition from conventional transistors to TFETs in future technology nodes.

- Compatibility with CMOS technology ensures that TFETs can be adopted without the need for entirely new manufacturing infrastructure, easing the pathway to scaling.

Applications in Advanced Computing:

- TFETs are well-suited for applications in advanced computing, such as neuromorphic computing, quantum computing, and energy-efficient artificial intelligence (AI) hardware.

- Their scaling potential and low-power operation make them ideal for these emerging technologies, which require high performance and energy efficiency at small scales.

Also, Read: Solid-State Batteries: Unleashing the Power of Tomorrow

Miniaturization Advantages of TFETs

Tunnel Field-Effect Transistors (TFETs) offer significant advantages in the miniaturization of electronic devices. These advantages stem from the unique operating principles of TFETs, which leverage quantum tunneling rather than thermionic emission for current transport. As a result, TFETs can achieve efficient performance at reduced dimensions, making them ideal for the next generation of ultra-scaled electronic devices. Here are the key miniaturization advantages of TFETs:

1. Reduced Short-Channel Effects

Short-Channel Effects (SCEs):

- In conventional MOSFETs, as the channel length decreases, short-channel effects such as threshold voltage roll-off, drain-induced barrier lowering (DIBL), and increased leakage currents become more pronounced.

- These effects degrade the performance and reliability of MOSFETs at smaller scales.

TFETs and SCEs:

- TFETs are less susceptible to short-channel effects because their operation is based on quantum tunneling rather than thermionic emission.

- The tunneling mechanism is less influenced by the physical dimensions of the channel, allowing TFETs to maintain performance even as device dimensions shrink.

- This makes TFETs more suitable for miniaturization, enabling the development of smaller, more efficient transistors.

2. Lower Subthreshold Swing

Subthreshold Swing (SS):

- Subthreshold swing is a measure of how effectively a transistor can switch from the off state to the on state. A lower SS indicates a sharper transition and more efficient switching.

- In conventional MOSFETs, the subthreshold swing is limited by thermal effects, typically around 60 mV/decade.

TFETs’ Advantage:

- TFETs can achieve subthreshold swings lower than the 60 mV/decade limit due to their quantum tunneling mechanism.

- A lower SS allows TFETs to switch more efficiently at lower voltages, which is critical for maintaining performance in miniaturized devices.

- This results in lower power consumption and reduced leakage currents, enhancing the energy efficiency of scaled-down transistors.

3. Enhanced Scalability

Scalability Issues in MOSFETs:

- As MOSFETs are scaled down, issues such as increased leakage currents, higher power consumption, and difficulty in maintaining electrostatic control become more challenging.

TFETs’ Scalability:

- TFETs offer better scalability due to their reduced sensitivity to short-channel effects and lower subthreshold swing.

- The ability to operate efficiently at smaller scales makes TFETs ideal for future technology nodes, where continued miniaturization is essential.

- TFETs can support the continuation of Moore’s Law, which predicts the doubling of transistors on a chip approximately every two years.

4. Power Efficiency

Low-Voltage Operation:

- TFETs can operate at much lower supply voltages compared to MOSFETs, significantly reducing power consumption.

- Lower operating voltages are crucial for miniaturized devices, where power efficiency is a key consideration.

Reduced Leakage Currents:

- The lower off-state leakage current of TFETs contributes to lower standby power consumption, which is especially important for battery-operated and portable devices.

- This enhances the overall energy efficiency of miniaturized electronic systems, enabling longer battery life and reduced energy costs.

Also, Read: Unveiling Supercapacitors: Revolutionizing Energy Storage

5. Flexibility in Material and Design

Material Selection:

- TFETs can utilize a variety of semiconductor materials, including advanced materials such as III-V compounds, germanium, and two-dimensional materials like graphene.

- This flexibility allows for the optimization of the tunneling process, enhancing performance at reduced dimensions.

Innovative Designs:

- Novel TFET architectures, such as vertical TFETs, gate-all-around (GAA) TFETs, and nanowire TFETs, provide additional pathways for miniaturization.

- These designs offer improved electrostatic control and reduced leakage, making them well-suited for ultra-scaled devices.

6. Applications in Advanced Technologies

Portable Electronics:

- Miniaturized TFETs can be integrated into smartphones, tablets, and wearable devices, where space is limited and power efficiency is critical.

- The reduced size and enhanced performance of TFETs support the development of more compact and powerful portable electronics.

Internet of Things (IoT):

- IoT devices often require small, energy-efficient components. TFETs’ miniaturization advantages make them ideal for sensors, actuators, and other IoT applications.

- The ability to maintain performance at reduced dimensions enables the deployment of IoT devices in a wider range of environments and applications.

Medical Devices:

- Miniaturized TFETs can be used in medical implants and wearable health monitors, where size and power consumption are critical constraints.

- The enhanced performance and reduced power requirements of TFETs support the development of more effective and user-friendly medical devices.

Challenges in Manufacturing TFETs

Tunnel Field-Effect Transistors (TFETs) offer significant advantages over conventional transistors, particularly in terms of energy efficiency and scalability. However, the manufacturing of TFETs presents several challenges that need to be addressed to realize their full potential in commercial applications. These challenges include material selection, fabrication complexity, process integration, variability, and reliability issues.

1. Material Selection

Heterojunction Requirement:

- TFETs often require heterojunctions, where different semiconductor materials are used for the source and channel regions to optimize band alignment and enhance tunneling efficiency.

- Selecting appropriate materials with complementary properties (e.g., suitable bandgap energies and effective masses) is crucial but challenging.

Advanced Materials:

- While materials like III-V compounds (e.g., InAs, GaSb) offer superior tunneling properties, they are more complex and expensive to work with compared to silicon.

- Developing reliable and cost-effective methods to integrate these advanced materials with existing silicon technology remains a significant hurdle.

2. Fabrication Complexity

Epitaxial Growth:

- The precise growth of high-quality heterojunctions requires advanced epitaxial techniques, such as molecular beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD).

- These processes are not only complex and costly but also require stringent control over temperature, pressure, and chemical environments to ensure the desired material properties.

Interface Quality:

- Achieving high-quality interfaces between different materials is critical for the performance of TFETs. Any defects, roughness, or impurities at the interfaces can significantly degrade tunneling efficiency and device performance.

- Controlling and minimizing interface defects during fabrication is a major challenge.

3. Process Integration

Compatibility with CMOS Technology:

- Integrating TFETs with existing CMOS (Complementary Metal-Oxide-Semiconductor) fabrication processes is essential for their commercial adoption.

- Differences in material systems, thermal budgets, and processing steps between TFETs and conventional MOSFETs complicate the integration process.

- Developing a seamless integration approach that leverages the strengths of both technologies without introducing significant process complexity or yield loss is crucial.

Scaling Down:

- As device dimensions shrink, maintaining the performance and reliability of TFETs becomes increasingly challenging.

- Ensuring that the tunneling junctions and overall device structure remain effective at nanometer scales requires innovative design and fabrication solutions.

4. Variability and Yield

Manufacturing Variability:

- Variations in material properties, doping concentrations, and interface quality can lead to significant variability in TFET performance.

- Controlling these variations to ensure consistent device behavior across large-scale manufacturing is a critical challenge.

Yield Issues:

- The complexity of TFET fabrication processes can result in lower yields compared to conventional MOSFETs.

- Defects introduced during epitaxial growth, material deposition, and patterning steps can adversely affect yield, making large-scale production economically challenging.

5. Reliability and Stability

Long-Term Reliability:

- Ensuring the long-term reliability of TFETs under various operating conditions is essential for their practical application.

- Potential reliability issues include degradation of material interfaces, electromigration, and thermal stability.

Thermal Management:

- While TFETs typically operate at lower power levels, managing heat dissipation in densely packed circuits is still a concern, especially as device dimensions shrink.

- Effective thermal management solutions are necessary to maintain device performance and longevity.

6. Cost Considerations

High Fabrication Costs:

- The advanced materials and fabrication techniques required for TFETs are generally more expensive than those used for traditional silicon-based MOSFETs.

- Reducing these costs through process optimization and economies of scale is necessary for TFETs to become commercially viable.

Research and Development Investment:

- Significant investment in research and development is required to overcome the various technical challenges associated with TFET fabrication.

- Collaboration between academia, industry, and government institutions is vital to drive innovation and reduce the time-to-market for TFET technologies.

Also, Read: Gamechanger: Sodium-ion batteries may make EVs far more affordable

Importance of Choosing the Right Materials for TFETs

The choice of materials in Tunnel Field-Effect Transistors (TFETs) is a critical factor that significantly influences their performance, efficiency, and scalability. The unique operating principles of TFETs, which rely on quantum tunneling, require careful selection of materials to optimize the tunneling process and overall device characteristics. Here, we explore the importance of choosing the right materials for TFETs and the key considerations involved.

1. Bandgap Engineering

Optimal Bandgap for Tunneling:

- The bandgap of the semiconductor materials used in TFETs determines the alignment of energy bands, which is crucial for efficient tunneling.

- Materials with appropriate bandgaps can create a smaller tunneling barrier, facilitating easier carrier injection and improving on-state current (I<sub>ON</sub>).

Heterojunction Advantage:

- Using different materials for the source and channel (heterojunction TFETs) allows for better band alignment compared to homojunction TFETs (same material throughout).

- Heterojunctions can be engineered to have staggered or broken band alignments, enhancing the tunneling probability and device performance.

2. High Carrier Mobility

Enhanced Performance:

- High carrier mobility in the channel material is essential for achieving high-speed operation and low power consumption.

- Materials with high electron or hole mobility reduce scattering and resistance, enabling faster switching and higher drive currents.

Material Examples:

- III-V compounds such as indium arsenide (InAs) and gallium antimonide (GaSb) are known for their high electron and hole mobilities, making them excellent candidates for TFETs.

- Germanium (Ge) and two-dimensional materials like graphene also offer high mobility, contributing to improved device performance.

3. Effective Mass of Carriers

Influence on Tunneling:

- The effective mass of charge carriers affects the tunneling probability. Lower effective mass leads to higher tunneling rates, enhancing the overall performance of the TFET.

- Selecting materials with lower effective masses for electrons or holes can significantly improve the subthreshold swing and on-state current.

Balancing Bandgap and Effective Mass:

- While low effective mass is desirable, it must be balanced with the appropriate bandgap to avoid excessive leakage currents and maintain device stability.

- Material combinations in heterojunction TFETs are often optimized to achieve this balance.

4. Interface Quality and Compatibility

Minimizing Interface Defects:

- The quality of the interface between different materials in a TFET is critical for minimizing defects that can trap carriers and degrade performance.

- Smooth, defect-free interfaces ensure efficient tunneling and reduce scattering, enhancing the overall device efficiency.

Lattice Matching:

- Lattice matching between different materials is important to reduce strain and dislocations at the interface.

- Materials with similar lattice constants are preferred to minimize defects and ensure high-quality epitaxial growth.

Thermal Compatibility:

- Materials used in TFETs must be thermally compatible to withstand processing temperatures without degrading.

- Thermal expansion coefficients should be matched to avoid stress and potential damage during thermal cycling.

5. Scalability and Fabrication Compatibility

CMOS Integration:

- For widespread adoption, TFET materials need to be compatible with existing CMOS fabrication processes.

- Silicon-based TFETs or hybrid approaches that integrate advanced materials with silicon substrates can facilitate easier integration and lower manufacturing costs.

Advanced Materials:

- While III-V materials and two-dimensional materials offer superior performance, their integration into silicon-based processes presents challenges.

- Ongoing research aims to develop methods for integrating these materials into standard fabrication workflows.

6. Environmental and Economic Considerations

Material Availability and Cost:

- The availability and cost of materials are important considerations for large-scale manufacturing.

- While advanced materials like III-V compounds offer performance benefits, they are often more expensive and less abundant than silicon.

Sustainability:

- The environmental impact of material extraction, processing, and disposal should be considered.

- Sustainable material choices and efficient fabrication processes can reduce the environmental footprint of TFET production.

Current Limitations in Material Technology for TFETs

While Tunnel Field-Effect Transistors (TFETs) offer significant potential for low-power and high-efficiency applications, several material-related challenges still hinder their widespread adoption and performance optimization. These limitations include issues related to material selection, interface quality, fabrication complexity, and reliability. Here, we discuss the key limitations in material technology for TFETs.

1. Material Selection and Bandgap Engineering

Bandgap Mismatch:

- Achieving the optimal band alignment for efficient tunneling is crucial. However, finding material pairs with the desired bandgap and band alignment for heterojunction TFETs is challenging.

- III-V compounds such as InAs and GaSb provide suitable properties, but integrating these materials into silicon-based processes poses significant difficulties.

Limited Material Choices:

- While silicon is the most widely used semiconductor, its indirect bandgap and relatively high effective mass limit its tunneling efficiency. Alternatives like III-V materials or two-dimensional materials are better suited but are not as mature in terms of integration with existing silicon technology.

2. Interface Quality and Defects

Interface Defects:

- High-quality interfaces between different materials are essential for efficient tunneling and overall device performance. Any defects or roughness at the interfaces can trap carriers, increase scattering, and degrade the TFET’s performance.

- Achieving defect-free interfaces in heterojunction TFETs is particularly challenging due to lattice mismatches and thermal expansion differences between materials.

Surface Roughness:

- Surface roughness at the interfaces can significantly affect the tunneling process. Even minor imperfections can lead to increased resistance and reduced current flow, impacting the device’s efficiency.

3. Fabrication Complexity

Advanced Epitaxial Growth:

- Techniques like molecular beam epitaxy (MBE) and metal-organic chemical vapor deposition (MOCVD) are used to grow high-quality heterojunctions. These methods require precise control over temperature, pressure, and chemical environment, making them complex and costly.

- Ensuring uniform material quality over large wafers is difficult, which affects scalability and manufacturing yield.

Integration with CMOS Processes:

- Integrating advanced materials such as III-V compounds with traditional silicon-based CMOS processes is challenging due to differences in processing temperatures, chemical compatibility, and mechanical properties.

- Developing hybrid processes that can seamlessly incorporate these materials without compromising the integrity of the existing silicon infrastructure remains a significant hurdle.

4. Thermal and Mechanical Stability

Thermal Mismatch:

- Differences in thermal expansion coefficients between materials can cause stress and defects during fabrication and operation. This stress can lead to dislocations, cracks, and other defects that degrade device performance and reliability.

Mechanical Stability:

- Maintaining mechanical stability in flexible or stretchable TFETs, which use advanced materials like graphene or other 2D materials, is challenging. Ensuring these materials can withstand mechanical deformation while maintaining high performance is crucial for applications in wearable and flexible electronics.

5. Reliability and Longevity

Material Degradation:

- Some advanced materials, such as III-V compounds, are more susceptible to environmental degradation (e.g., oxidation, moisture absorption) than silicon. Ensuring long-term stability and reliability of these materials in real-world conditions is a challenge.

Electromigration and Thermal Stability:

- Electromigration, which is the movement of metal atoms caused by the momentum transfer from electrons, can be more pronounced in materials with high current densities. This issue affects the longevity and reliability of TFETs, especially under high-stress conditions.

6. Cost and Availability

High Material Costs:

- Advanced materials like III-V semiconductors and 2D materials are generally more expensive than silicon due to their complex fabrication processes and limited availability.

- The high cost of these materials can be a barrier to large-scale production and commercial viability.

Scalability Issues:

- Scaling up the production of high-quality heterojunctions or 2D materials to meet the demands of the semiconductor industry is challenging. Ensuring consistent quality and performance across large wafer areas is necessary for practical applications.

Performance at High Current Levels in TFETs

Tunnel Field-Effect Transistors (TFETs) offer significant advantages in terms of low power consumption and scalability, making them attractive for various applications. However, one of the critical challenges for TFETs is their performance at high current levels. Here we explore the factors affecting TFET performance at high current levels, the limitations, and ongoing research aimed at addressing these issues.

1. Factors Affecting High Current Performance

Tunneling Current:

- In TFETs, the on-state current (𝐼𝑂𝑁ION) is primarily driven by the quantum tunneling of carriers (electrons or holes) through a potential barrier.

- The efficiency of this tunneling process determines the maximum current that can be achieved.

Material Properties:

- The choice of materials for the source, channel, and drain significantly impacts the tunneling efficiency and, consequently, the high current performance.

- Materials with high mobility and appropriate band alignment can enhance the on-state current but finding optimal material combinations remains challenging.

Device Architecture:

- The design of the TFET, including the dimensions of the channel and the alignment of energy bands, plays a crucial role in determining the current levels.

- Advanced architectures such as heterojunction TFETs, gate-all-around (GAA) structures, and vertical TFETs are being explored to improve high current performance.

2. Limitations at High Current Levels

Lower On-State Current:

- Compared to traditional MOSFETs, TFETs generally exhibit lower on-state currents due to the inherent limitations of the tunneling mechanism.

- The tunneling current is highly sensitive to the alignment of the energy bands, and even small deviations can significantly impact the current levels.

Series Resistance:

- High series resistance in the source and drain regions can limit the overall current that flows through the TFET.

- Reducing series resistance through material engineering and optimized device design is crucial for enhancing high current performance.

Thermal Management:

- As the current increases, so does the heat generated within the TFET. Efficient heat dissipation is essential to prevent thermal degradation and maintain device reliability.

- Advanced cooling techniques and thermal management strategies are necessary to handle the increased thermal load at high current levels.

Scaling Challenges:

- Scaling down the dimensions of TFETs to achieve higher integration densities can exacerbate issues related to high current performance, such as increased leakage currents and reduced drive strength.

- Balancing the trade-offs between miniaturization and high current performance is a key challenge in TFET development.

3. Ongoing Research and Solutions

Material Engineering:

- Researchers are investigating novel materials with higher mobility and better band alignment to enhance tunneling efficiency. III-V compounds, two-dimensional materials, and novel heterostructures are being explored to improve high current performance.

- Doping techniques and material modifications are being used to reduce series resistance and enhance carrier injection.

Device Design Innovations:

- Advanced TFET architectures, such as vertical TFETs, gate-all-around (GAA) structures, and nanowire TFETs, are being developed to improve electrostatic control and increase on-state current.

- Optimizing the geometry and layout of TFETs can help reduce parasitic resistances and enhance current flow.

Interface Engineering:

- Improving the quality of interfaces between different materials in heterojunction TFETs is critical for reducing scattering and enhancing tunneling efficiency.

- Techniques such as atomic layer deposition (ALD) and molecular beam epitaxy (MBE) are being used to create high-quality interfaces with minimal defects.

Thermal Management Solutions:

- Advanced thermal management techniques, including the use of heat spreaders, thermal vias, and innovative cooling solutions, are being explored to handle the increased heat generation at high current levels.

- Incorporating materials with high thermal conductivity into the device structure can help dissipate heat more effectively.

Simulation and Modeling:

- High-fidelity simulation tools are being developed to model the complex physics of TFETs at high current levels. These simulations help optimize device design and predict performance under various operating conditions.

- Understanding the impact of various parameters on high current performance through simulation can guide experimental efforts and accelerate the development of high-performance TFETs.

Trade-offs Between Power and Performance in TFETs

Tunnel Field-Effect Transistors (TFETs) present a compelling alternative to traditional transistors like MOSFETs, especially in terms of energy efficiency and scalability. However, optimizing TFETs for both power and performance involves several trade-offs. Understanding and managing these trade-offs is crucial for effectively integrating TFETs into various applications. Here, we explore the key trade-offs between power and performance in TFETs.

1. Power Consumption vs. On-State Current (I<sub>ON</sub>)

Low Power Operation:

- One of the primary advantages of TFETs is their ability to operate at lower supply voltages, significantly reducing power consumption.

- This makes TFETs ideal for applications where energy efficiency is critical, such as portable devices, IoT sensors, and wearable electronics.

Challenge with On-State Current:

- The quantum tunneling mechanism in TFETs generally results in lower on-state currents than MOSFETs.

- Achieving high on-state currents typically requires optimizing the material properties and device structure, which can increase complexity and cost.

Trade-off:

- Reducing power consumption often comes at the expense of lower on-state current. Enhancing the on-state current to match MOSFET levels while maintaining low power operation remains a significant challenge.

- Researchers are exploring advanced materials and innovative device architectures to balance this trade-off, but improvements in one area often result in compromises in the other.

2. Subthreshold Swing vs. Switching Speed

Subthreshold Swing (SS):

- TFETs can achieve subthreshold swings lower than the 60 mV/decade limit of MOSFETs, allowing for more efficient switching at lower voltages.

- A lower SS improves the overall energy efficiency of the device and reduces leakage currents in the off state.

Switching Speed:

- While a lower SS indicates sharp switching characteristics, the absolute switching speed can be limited by the tunneling process.

- The tunneling current is highly sensitive to the alignment of the energy bands, and achieving high-speed operation can be challenging.

Trade-off:

- Optimizing TFETs for a low subthreshold swing can sometimes result in slower switching speeds, especially if the tunneling mechanism is not sufficiently optimized for rapid current changes.

- Balancing the need for a low SS with the requirement for high-speed switching is essential for applications in high-performance computing and fast signal processing.

3. Material Quality vs. Fabrication Complexity

High-Quality Materials:

- Advanced materials such as III-V compounds, germanium, and two-dimensional materials offer superior electronic properties, enhancing tunneling efficiency and overall device performance.

- High-quality interfaces and precise material control are essential for maximizing the benefits of these materials.

Fabrication Challenges:

- Integrating these materials into existing silicon-based CMOS processes is complex and expensive.

- High-quality epitaxial growth techniques and interface engineering are required, which increase fabrication complexity and cost.

Trade-off:

- Utilizing high-quality materials can significantly improve TFET performance, but at the cost of increased fabrication complexity and potentially lower manufacturing yields.

- Finding a balance between material quality and fabrication feasibility is crucial for the commercial viability of TFETs.

4. Device Scalability vs. Thermal Management

Scalability: